MATLAB Coder

从 MATLAB 代码生成 C 和 C++ 代码

结合 Embedded Coder®,MATLAB Coder 还支持代码自定义、特定于目标的优化、代码可追溯性以及软件在环 (SIL) 和处理器在环 (PIL) 验证。

要将 MATLAB 程序部署为独立应用程序,请使用 MATLAB Compiler™。要生成软件组件,以便与其他编程语言集成,请使用 MATLAB Compiler SDK™。

随时随地运行无阻

生成可读可移植的 ANSI C/C++ 源代码,并且免版权费。

免版权费部署算法

您可以使用任何 C/C++ 编译器编译代码,并可以在包括桌面系统、移动设备到嵌入式硬件在内的任何硬件上运行生成的代码。生成的代码免版权费,您可将其免费部署到面向客户的商用应用。

MATLAB Coder 成功案例

了解各行各业的工程师和科学家如何使用 MATLAB Coder 为应用生成 C/C++ 代码。

支持的工具箱和函数

MATLAB Coder 可从多种 MATLAB 语言功能生成代码,设计工程师基于这些功能开发算法以用作大型系统组件。该产品支持来自 MATLAB 以及配套工具箱的超过 2,500 个运算符和函数。

从 MATLAB 部署 C++ 代码

将生成的代码与面向对象的 C++ 源代码集成。

使用命名空间生成 C++ 代码

MATLAB Coder 可以生成包含在命名空间中的 C++ 代码,以便您将其轻松集成到可能具有同名函数或同名数据类型的其他源代码。代码生成器会将所有生成的函数和类型定义打包到命名空间。

从 MATLAB 类生成 C++ 类

MATLAB Coder 可从 MATLAB 代码中的类生成 C++ 类,包括值类、句柄类和 System object。生成的代码可以编译为 C++ 库或可执行文件,还可以集成到您的现有 C++ 源代码。

在生成的函数接口使用动态分配的 C++ 数组

如果某一 MATLAB 函数接受或返回编译时大小未知的数组,或其边界超出预定义的阈值,您也可以为其生成 C++ 代码。在生成的代码中,数组具有动态内存分配,以名为 coder::array 的类模板实现。coder::array 可对异常安全代码取消内存分配,还提供 API 来访问和管理动态数组。

部署深度学习网络和机器学习模型

从经过训练的深度学习网络和机器学习模型生成代码。

部署端到端深度学习算法

将多种经过训练的深度学习网络(如 ResNet-50 和 MobileNet-v2)以及各类网络层(如 LSTM)从 Deep Learning Toolbox™ 部署到 Intel® 和 ARM® Cortex® CPU。除了经过训练的深度学习网络,您还可以同时为预处理和后处理生成代码,以部署完整的算法。

针对深度学习推断生成优化代码

由于 MATLAB Coder 仅生成特定算法运行推断所需的代码,因此该代码相比其他深度学习解决方案运行更快、内存占用量更少。生成的代码会调用优化的库,包括针对 Intel 处理器的 Intel MKL-DNN,以及针对 ARM Cortex 处理器的 ARM Compute Library。使用 GPU Coder™ 生成可在现代 NVIDIA® GPU 上运行的 CUDA® 代码,从而加速或部署算法。

部署端到端机器学习模型

为包括预处理和后处理在内的整个机器学习算法生成 C/C++ 代码,以部署统计和机器学习模型。更新已部署模型的参数,而无需重新生成 C/C++ 预测代码。

硬件原型

将算法自动转换为 C/C++ 语言以快速在硬件上实现。

桌面和云平台原型实现

使用 MATLAB Coder 或等效命令行函数为信号处理、计算机视觉、深度学习、控制系统或其他应用快速生成代码,然后针对硬件编译代码。

嵌入式和移动平台原型实现

将生成的代码手动集成到您的应用,以在各种目标设备上实现。针对 Raspberry Pi,借助 MATLAB Support Package for Raspberry Pi Hardware 自动化该过程。

从原型到生产

将 MATLAB Coder 和 Embedded Coder 结合使用,可在生成的代码中有效利用特定于处理器的内部函数,这些函数的执行速度快于标准 ANSI/ISO C/C++ 代码。

与软件集成

在软件环境中以 C/C++ 代码形式重用 MATLAB 算法。

生成接口简单、易于集成的代码

生成的代码以自然的方式使用 C/C++ 类型,简化了集成到外部代码的过程。您可以将生成的代码作为源代码或库进行集成。您可以在 MATLAB 中引入受信任的 C/C++ 库或组件以执行保真度更高的测试,并可从生成的代码中自动调用它们。

优化所生成代码的性能

应用优化以在执行速度、内存使用量、可读性和可移植性之间进行权衡。使用分析工具确定瓶颈。要进一步提升性能,请生成多核 OpenMP 代码并调用 LAPACK、BLAS 和 FFTW 等优化库(如有)。

在集成前对生成的代码重用 MATLAB 测试

重用现有 MATLAB 测试以在交互式 MATLAB 环境中验证所生成代码的行为。使用 MATLAB 单元测试框架快速开发一组功能丰富的回归测试,以用于验证生成的 C/C++ 代码。

加速算法

生成 C/C++ 代码并进行编译,以在 MATLAB 内使用。

在 CPU 上加速算法

您可以从 MATLAB 代码以 MEX 函数的形式调用生成的代码以加速执行,不过性能将因 MATLAB 代码本身的特性而异。您可以分析所生成的 MEX 函数,以确定瓶颈并重点优化。

使用 GPU 加速算法

使用 Parallel Computing Toolbox™ 加速在 MATLAB 中运行的算法。使用 GPU Coder 生成可在现代 NVIDIA GPU 上运行的 CUDA 代码,以便进行加速或部署。

Embedded Coder

生成针对嵌入式系统优化的 C 和 C++ 代码

Embedded Coder 为 AUTOSAR、MISRA C® 和 ASAP2 软件标准提供内置支持。它还提供可追溯性报告、代码文档记录和自动化软件验证功能,以支持 DO-178、IEC 61508 和 ISO 26262 软件开发。Embedded Coder 代码可移植,并且可在任何处理器上编译和执行。此外,Embedded Coder 为特定硬件提供了包含高级优化和设备驱动程序的支持软件包。

了解各家公司如何使用 Embedded Coder 生成产品级代码,用于控制、信号处理、图像处理和计算机视觉以及机器学习应用。

SUPPORT PACKAGE

Component Deployment Guidelines for Embedded Coder

配置以生成代码

要为 Embedded Coder® 配置代码生成设置,请使用 MATLAB Coder(针对 MATLAB®)或 Embedded Coder Quick Start(针对 Simulink)。您也可以使用 MATLAB 命令和脚本直接配置每项设置。 通过 MATLAB Coder,您可以: 为 MATLAB 文件和函数生成代码 选择处理器和代码生成输出 选择 Embedded Coder 优化 通过针对 Simulink 的 Embedded Coder Quick Start,您可以: 为 Simulink 模型和子系统生成代码 选择处理器和代码生成输出 选择 Embedded Coder 以优化 RAM 或执行速度

选择目标

Embedded Coder 使用配置对象和系统目标文件,将 MATLAB 代码和 Simulink 模型转换为产品级源代码和可执行文件。

对于 MATLAB,指定以下输出目标之一: MEX 文件 C/C++ 静态库 C/C++ 可执行文件 对于 Simulink,指定即用型配置之一,包括: 嵌入式实时目标 — 生成支持浮点和定点数据的 ANSI/ISO C、C++ 和封装 C++ 代码,以便在各类产品级处理器上高效实时执行 AUTOSAR 目标 — 生成支持 AUTOSAR 软件组件开发的 C 代码和运行时接口(需要 AUTOSAR Blockset) 共享库目标 — 以 Windows® 动态链接库 (.dll) 文件或 UNIX® 共享对象 (.so) 文件的形式,生成代码的共享库版本以供主机平台执行 另外,借助来自 MathWorks 和第三方的 MATLAB 附加功能,您可以扩展 Embedded Coder 的功能以支持特定硬件,包括 ARM®、Intel®、NXP™、STMicroelectronics® 和 Texas Instruments™。

使用自定义数据

Embedded Coder 允许您定义和控制模型数据在所生成代码中的出现方式,以便进行软件集成。 对于 MATLAB 代码,Embedded Coder 支持所有 MATLAB Coder 数据定义,包括定点对象和预定义的存储类。 对于 Simulink 模型,Embedded Coder 支持以下数据字典和设定功能: Embedded Coder 字典 — 允许您查看和自定义代码定义,包括函数接口、存储类和内存区段 Simulink 数据对象 — 提供预定义存储类,包括常量、volatile 变量、导出的全局变量、导入的全局变量、定义指令、结构、位字段(包括位压缩结构)以及 get 和 set 访问方法 模块压缩数据对象 — 为通常用于大规模生产的高级数据对象(如用于标定或调节查找表的内存段)提供预配置属性 用户数据类型 — 允许您为复杂数据创建抽象类型,以便精确控制模型数据在所生成代码中的出现方式,结合已有数据,以及扩展或替换 Simulink 内置类型 Embedded Coder 支持您访问 Simulink 中的 ASAP2 数据交换文件,以便您使用 ASAP2 标准导出包含复杂数据定义的模型数据。您可以修改内置功能以生成其他数据交换机制。

优化和打包代码

使用 Embedded Coder,您可以控制函数边界、保留表达式并对多个模块应用优化以进一步缩小代码体积。与所生成代码之间的数据交换通过全局变量或函数参数实现。您可以从生成的代码追踪到模型中的模块和信号。 Embedded Coder 提供针对 MATLAB 代码和 Simulink 模型的代码生成选项,支持: 为数学函数和运算符生成特定于处理器的代码 重用代码以导出到已有环境或外部环境 消除不必要的初始化、终止、记录和错误处理代码 从仅限整数的应用程序中删除浮点代码 此外还针对 Simulink 模型提供额外的 Embedded Coder 优化和配置选项,支持: 使用宏生成代码变体以用于预处理器编译 控制每个生成的文件的格式 确定全局数据的定义和引用方式 指定注释的内容和放置

代码的注释、追踪和文档记录

Embedded Coder 提供了几种功能,用于检查为 MATLAB 文件和函数或 Simulink 模型和子系统所生成的代码。使用这些功能,您可以: 生成描述代码模块、函数接口和静态代码度量指标的代码报告 控制生成的全局数据、数据类型和函数的标识符格式 在生成的代码中以注释形式包含 MATLAB 代码,包括函数帮助文本 结合 Simulink,Embedded Coder 还可以插入高层级需求作为代码注释,并包含指向需求来源的链接(需要 Requirements Toolbox™)。Simulink 代码生成的代码报告还包括代码接口描述、可追溯性报告以及生成的源文件和代码的显示。模型与生成的代码之间存在双向链接,方便您在每行代码与对应的 Simulink 模型元素(包括子系统、模块、MATLAB 函数和代码以及 Stateflow® 图和转移)之间导航。

执行和验证代码

Embedded Coder 支持您将生成的代码纳入代码执行环境。 对于 MATLAB,从 Embedded Coder 生成的代码通过 MATLAB Coder 提供的同一执行框架来执行。 对于 Simulink,Embedded Coder 极大扩展了 Simulink Coder 提供的实时执行框架。默认情况下,代码可以在使用或不使用实时操作系统 (RTOS) 的情况下执行,并可在单任务、多任务、多核或异步模式下执行。您还可以使用 Embedded Coder 进行软件在环 (SIL) 和处理器在环 (PIL) 测试来验证代码执行结果。借助 Simulink Test™ 和 Simulink Coverage,您可以将测试执行、结果比较和覆盖率分析自动化。您还可以对代码执行开展性能分析。

生成主程序

Embedded Coder 基于您为在实时环境中部署代码而提供的信息生成可扩展的主程序。借助此功能,您可以从模型生成和构建完整的自定义可执行文件。

执行多速率、多任务和多核代码

Embedded Coder 使用模型中指定的周期采样次数生成单速率或多速率代码。对于多速率、多任务模型,它采用一种名为速率分组的策略,该策略分别为模型中的基本速率任务和每个子速率任务生成单独的函数。您还可以使用 Simulink 并行执行建模生成多线程代码以用于多核处理。

执行 SIL 和 PIL 测试

Embedded Coder 使用 Simulink 仿真模式或 S-function 模块,在 Simulink 中自动执行生成的代码以进行 SIL 测试,或在嵌入式目标上自动执行生成的代码以进行 PIL 测试。借助 Simulink Test™,您可以自动执行测试,并将测试结果与来自原始模型的仿真结果进行比较。通过 Simulink Coverage 或与第三方工具集成,您可以进行结构性的代码覆盖率分析以衡量测试的完整性。代码性能分析则可提供主机或目标处理器上的执行时间。

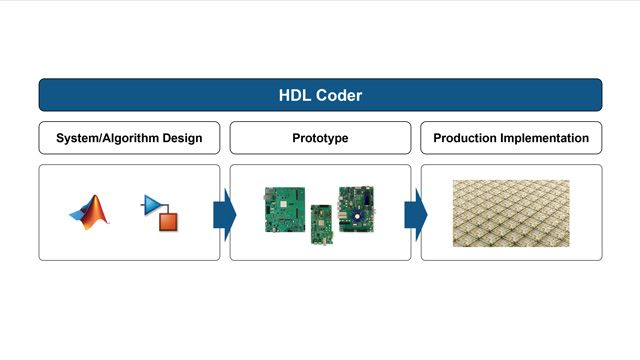

HDL Coder

生成用于 FPGA 和 ASIC 设计的 VHDL 和 Verilog 代码。

HDL Coder 包括工作流顾问,可用于在 Xilinx®、Intel® 和 Microchip 板上通过生成的代码自动进行原型构建,并为 ASIC 和 FPGA 工作流生成 IP 核。您可以以速度和面积为目的进行优化,突出显示关键路径,并在综合之前生成资源利用率估计值。HDL Coder 提供 Simulink 模型与生成的 Verilog 和 VHDL 代码之间的可追溯性,因此支持对遵循 DO-254 及其他标准的高完整性应用进行代码验证。

高层硬件设计

使用 300 多个支持 HDL 的 Simulink 模块和 MATLAB 函数设计您的子系统;添加 Stateflow 图、Simscape™ 模型和深度学习网络。对您的设计的硬件行为进行仿真,探索替代架构,并使用定点或浮点数据类型或结合使用两者来生成可综合的 VHDL 或 Verilog 代码。

独立于供应商的目标部署

生成对领先供应商的 FPGA 进行了目标优化的可综合 RTL 代码。生成的代码同样可用于 ASIC 硬件。重用相同的模型来生成原型和产品级代码。

设计优化

在进行 RTL 实现之前探索各种硬件架构和定点量化选项。使用高级综合优化,如资源共享、流水线化和延迟平衡,高效地映射到逻辑、DSP 和 RAM 等设备资源。

基于 FPGA 的设备

生成高效映射到 Xilinx、Intel 和 Microchip FPGA 及 SoC 设备的 RTL 代码。使用热门板的硬件支持包将输入和输出映射到设备级 I/O 和 AXI 寄存器,或定义您自己的自定义参考设计。

ASIC 工作流

设计并在包含模拟、数字和软件的混合系统的环境中验证您的架构和高层硬件功能。生成具有高结果质量 (QoR) 的 RTL 代码,或生成可综合的 SystemC 代码以与 Cadence® Stratus HLS 结合使用。

应用开发

使用 Wireless HDL Toolbox™ 中的子系统和模块设计通信算法,或使用 Vision HDL Toolbox™ 开发视觉处理算法的流式实现。实现复杂的低延迟电机控制系统。

硬件设计

开发高效处理流数据的算法。使用支持 HDL 的 Simulink 模块、自定义 MATLAB Function 模块和 Stateflow 图添加硬件架构细节。

实时仿真和测试

使用 HDL 工作流顾问部署 Speedgoat 可编程 FPGA I/O 模块和类似的第三方模块,并使用 Simulink Real-Time™ 进行仿真。使用本机浮点 (9:19) HDL 代码生成来简化高准确度原型构建的工作流。

早期验证

与 HDL Verifier™ 结合使用以确保您生成的 RTL 代码将在其系统环境中按要求运行。使用与领先的 HDL 仿真器的协同仿真,通过 MATLAB 和 Simulink 测试平台验证生成的 HDL。使用 FPGA 在环测试验证您的设计在 FPGA 开发板上的实现。

HDL Verifier

使用 HDL 仿真器和 FPGA 板测试并验证 Verilog 和 VHDL

HDL Verifier 可为 RTL 测试平台和完整的通用验证方法 (UVM) 环境生成 SystemVerilog 验证模型。这些模型可在 Questa、Xcelium 和 Vivado 仿真器中以本机方式运行,或通过 SystemVerilog 直接编程接口 (DPI) 在 Synopsys® VCS® 中运行。

HDL Verifier 提供可通过 MATLAB 在 Xilinx、Intel® 和 Microchip 板上调试和测试 FPGA 实现的工具。您可以将探测器插入设计中并设置触发条件,以将内部信号上传到 MATLAB 中进行可视化和分析。

RTL 验证

使用 MATLAB 和 Simulink 测试平台通过与 HDL 仿真器的协同仿真来验证 ASIC 或 FPGA 的 HDL 代码。为单元级或芯片级测试中使用的验证环境生成 SystemVerilog 测试平台。

FPGA 原型构建、验证和测试

使用 FPGA 在环测试在 FPGA 开发板上执行基于硬件的验证。探测设计中的内部信号以调试硬件,并用 MATLAB 控制测试。

HDL 协同仿真

使用 MATLAB 和 Simulink 作为测试平台验证 HDL 代码。通过与包括 Siemens EDA 的 ModelSim 和 Questa、Cadence Xcelium 和 Xilinx Vivado 仿真器在内的 HDL 仿真器进行协同仿真将既有 HDL 集成到系统仿真中。

FPGA 在环

使用 MATLAB 和 Simulink 测试平台测试在 FPGA 板上执行的 HDL 实现。通过以太网、JTAG 或 PCI Express® 将您的主机自动连接到 Xilinx、Intel 和 Microchip FPGA 板。

生成 SystemVerilog DPI

从 MATLAB 函数或 Simulink 子系统生成 SystemVerilog DPI 组件以用于功能验证环境,包括 Synopsys VCS、Cadence Xcelium 和 Siemens EDA 提供的 ModelSim 或 Questa。

MATLAB:文档 | 示例 Simulink:生成 UVM 环境

从 Simulink 模型生成完整的通用验证方法 (UVM) 测试平台。生成 UVM 序列、记分板和预测变量,并将其纳入生产测试平台。

FPGA 数据采集

从在 FPGA 上执行的设计中捕获高速信号,并自动将其加载到 MATLAB 中进行可视化和分析。分析整个设计中的信号,以验证预期行为或调查异常情况。

AXI 管理器

通过 JTAG、以太网或 PCI Express 协议从 MATLAB 和 Simulink 访问板载内存。通过读写 AXI 寄存器以及在 MATLAB 和 Simulink 与板载内存位置间传输大型图像或信号文件来测试 FPGA 算法。

Filter Design HDL Coder

为定点滤波器生成 HDL 代码

使用 Filter Design HDL Coder

Filter Design HDL Coder™ 已与 DSP System Toolbox™ 集成,可提供统一的设计和实现环境。您可以通过以下方式之一设计滤波器并生成 VHDL 和 Verilog 代码:使用 MATLAB® 命令行;或者在 DSP System Toolbox 中使用 Filter Design and Analysis 应用程序或 Filter Builder 应用程序。

设计定点滤波器

Filter Design HDL Coder 的设计入口输入是可以通过以下两种方式之一创建的量化滤波器: 使用 DSP System Toolbox 设计并量化滤波器 使用 Signal Processing Toolbox™ 设计滤波器,然后使用 DSP System Toolbox 量化滤波器 Filter Design HDL Coder 支持多种重要滤波器结构,包括: 离散时间有限脉冲响应 (FIR),包括对称、反对称和转置结构 二阶节 (SOS) 无限脉冲响应 (IIR),包括直接 I型 I、直接 II 型和转置结构 多速率滤波器,包括级联积分梳状 (CIC) 内插器和抽取器、直接型 FIR 和转置 FIR 多相内插器和抽取器、FIR 保持器和线性内插器,以及 FIR 多相采样率转换器结构 分数延迟滤波器,包括 Farrow 结构 Filter Design HDL Coder 可以使用级联多速率和离散时间滤波器生成 HDL 代码。其中,每种单速率和多速率滤波器结构均支持定点和浮点(双精度)实现。此外,FIR 结构还支持无符号定点系数。

优化滤波器架构

为定点滤波器生成 HDL

您可以使用 Filter Design and Analysis 应用程序或 Filter Builder 应用程序为定点滤波器生成 VHDL 或 Verilog 代码。当使用上述任一应用程序生成 HDL 代码时,您可以设置 HDL 生成选项,以指定实现架构、选择端口数据类型、插入管道寄存器等等。其他选项可用来为您的滤波器 HDL 设计生成并配置测试平台。

自定义 VHDL 和 Verilog 代码

Filter Design HDL Coder 根据选项设置或属性名称和属性值对,为量化滤波器生成滤波器和测试平台 HDL 代码。通过这些设置可以: 命名语言元素 指定端口参数 使用高级 HDL 编码功能 所有属性均具有默认设置。您可以使用 Filter Design and Analysis 应用程序或 Filter Builder 应用程序调整设置,从而自定义 HDL 输出。通过这些应用程序可以设置与以下各项相关的属性: HDL 语言规范 文件名和位置规范 重置规范 HDL 代码优化 测试平台自定义

测试并合成生成的 HDL 代码

您可以生成 VHDL 或 Verilog 测试平台,仿真并测试生成的 HDL 代码。此外,还可以使用 HDL Verifier™ 生成 Simulink® 协同仿真块,将在 Simulink 中运行的行为滤波器模型和测试连接到在 Cadence® Incisive® 和 Xcelium™ 仿真器或 Mentor® ModelSim® 和 Questa® 仿真器中运行的已生成 HDL 代码。协同仿真可以直接比较生成的 HDL 代码结果与 Simulink 中运行的行为滤波器模型结果,从而简化滤波器设计验证过程。经过上述集成,您可以运用 MATLAB 和 Simulink 的高级分析和可视化功能来测试、调试及验证滤波器设计的 HDL 实现。

Fixed-Point Designer

对定点和浮点算法进行建模和优化

Fixed-Point Designer 提供的应用程序和工具可用于分析双精度算法,并将其转换为降精度浮点或定点。使用优化工具,您可以选择满足数值精度要求和目标硬件约束的数据类型。为了高效实现,您可以将运算量庞大的设计构造替换为硬件最优的模式,如压缩的查找表。

您可以直接从定点和浮点优化模型生成产品级 C 和 HDL 代码。

免费技术文章: int8 量化简介及其广泛运用于深度神经网络的原因

数据类型探索

探索浮点和定点数据类型,分析数值精度取舍。

定点规格

为设计指定各种定点属性,包括特定于应用的字长、二进制小数点定标、任意斜率与偏差定标,以及舍入和溢出模式等控制细节。

浮点仿真

在仿真和代码生成中,为非规范浮点数(如下溢为零)进行目标硬件行为仿真。使用 MATLAB® 和 Simulink® 中的 fp16 半精度数据类型对有限精度浮点进行仿真。

仪表化和可视化

借助整个模型范围内的自动仪表化收集仿真数据和统计量。收集范围数据来探索和分析您的设计。借助可视化来优化您的设计,以高效利用硬件资源。

推导范围分析

根据对设计的数学分析推导出信号范围,并确定最坏情况下的范围或边缘情形,而无需创建全面涵盖所有情形的仿真测试平台。使用推导范围可以确保您的设计能够预防或处理所有可能的溢出。

自动确定数据类型

使用定点和浮点数据类型量化和优化您的设计。

定点量化

在软件的引导下探索不同的定点数据类型及其对系统数值行为所产生的量化影响。观察设计中变量的动态范围,并确保转换后的算法在浮点表示和定点表示下具有一致的行为。

浮点量化

将双精度设计自动转换为单精度,并对单精度情形下有限精度浮点表示和量化的效应进行分析。

数据类型优化

自动遍历各种定点配置以选择最佳的异质数据类型,同时满足对系统数值行为的容差限制。该优化旨在使用定点数据类型将总位宽度降至最低,以实现高效设计。

嵌入式实现

探索实现设计时面临的取舍,并使用高效的嵌入式算法优化您的设计。

函数逼近和查找表压缩

借助最优查找表,以数学方法逼近复杂的函数(如 sqrt 和 exp)或复杂的子系统。通过优化数据点和数据类型,压缩现有查找表来减少内存使用量。

生成位真代码

在从仿真到代码生成(包括加速、处理器在环仿真和软件在环仿真)的整个过程中,确保基于模型的设计始终保持比特精度一致。基于位真表示分析和验证定点算法。从降精度设计(包括半精度型)生成高效的代码。

HDL 优化矩阵模块

定点 HDL 库包含一系列 Simulink 模块,可对线性方程组及核心矩阵运算(如 QR 分解)的设计模式进行建模,以在 FPGA 上获得高效硬件实现。使用 HDL Coder™ 为包含此类模块的设计生成 HDL 代码。

测试和调试

分析、测试和调试算法的数值行为。

溢出和精度损失检测

快速识别、跟踪并调试溢出、精度损失以及范围或精度浪费的问题来源,并将您的设计与理想的浮点行为进行对比。保持模型和代码的比特精度一致可以最大限度地发挥基于模型设计的众多优势,帮助您在工作流早期发现上述问题。

测试数值边缘情形

生成涵盖多种数值情形的定点和浮点值,例如接近边界的值和非规范数,以测试算法的边缘情形,实现数值一致。生成具有不同维度和复/实性、使用整数、浮点和定点数据类型的信号的组合。

GPU Coder

为 NVIDIA GPU 生成 CUDA 代码

您可以将 GPU Coder 与 Embedded Coder® 结合使用,以通过软件在环 (SIL) 测试和处理器在环 (PIL) 测试验证生成代码的数值行为。

生成快速、灵活的 CUDA 代码

生成优化的 CUDA 代码。免版权费部署代码。

免版权费部署算法

在主流 NVIDIA GPU 上编译和运行生成的代码,无论是桌面系统、数据中心还是嵌入式硬件皆可。生成的代码免版权费,您可将其免费部署到面向客户的商用应用。

GPU Coder 成功案例

了解各行各业的工程师和科学家如何使用 GPU Coder 为应用生成 CUDA 代码。

使用支持的工具箱和函数生成代码

GPU Coder 可使用多种 MATLAB 语言功能生成代码,设计工程师基于这些功能开发算法以用作大型系统组件。这包括来自 MATLAB 以及配套工具箱的数百个运算符和函数。

整合既有代码

使用既有代码集成功能,将受信任的或高度优化的 CUDA 代码整合到您的 MATLAB 算法中,以在 MATLAB 中进行测试。然后,您就可以从生成的代码调用这些 CUDA 代码。

从 Simulink 模型生成 CUDA 代码

在 Simulink 中创建模型并生成优化的 CUDA 代码。

运行仿真并为 NVIDIA GPU 生成优化的代码

您可以将 GPU Coder 与 Simulink Coder™ 结合使用,以在 NVIDIA GPU 上加速 Simulink 模型中 MATLAB Function 模块的计算密集型部分。然后,您可以从 Simulink 模型生成优化的 CUDA 代码,并将其部署到您的 NVIDIA GPU 目标。

部署端到端深度学习算法

Deep Learning Toolbox™ 提供各种经过训练的深度学习网络,包括 ResNet-50、SegNet 和 LSTM,您可以在 Simulink 模型中使用这些网络,并将其部署到 NVIDIA GPU。除了经过训练的深度学习网络,您还可以同时为预处理和后处理生成代码,以部署完整的算法。

记录信号、调整参数并验证代码的数值行为

您可以将 GPU Coder 与 Simulink Coder 结合使用,以使用外部模式仿真实时记录信号和调整参数。将 GPU Coder 与 Embedded Coder 结合使用,则可以运行软件在环测试和处理器在环测试,这些测试可以验证生成代码的数值行为是否与仿真的行为一致。

从深度学习网络生成 CUDA 代码

使用 Deep Learning Toolbox 部署经过训练的深度学习网络。

部署端到端深度学习算法

将 Deep Learning Toolbox 提供的各种经过训练的深度学习网络(包括 ResNet-50、SegNet 和 LSTM)部署到 NVIDIA GPU。您可以使用预定义的深度学习层,也可以针对特定应用自定义层。除了经过训练的深度学习网络,您还可以同时为预处理和后处理生成代码,以部署完整的算法。

针对推断生成优化代码

与其他深度学习解决方案相比,GPU Coder 生成的代码占用的内存较少,因为它仅生成您的算法运行推断所需的代码。生成的代码会调用优化的库,包括 TensorRT 和 cuDNN。

使用 TensorRT 进一步优化

生成代码以实现 NVIDIA TensorRT 集成,这是一个高性能的深度学习推断优化器和运行时环境。相比标准 FP32 数据类型,使用 INT8 或 FP16 数据类型可实现进一步的性能提升。

深度学习量化

量化您的深度学习网络,以减少内存使用并增强推断性能。使用深度网络量化器,对性能与推断准确性之间的权衡进行分析和可视化。

优化生成的代码

GPU Coder 可自动优化所生成的代码。使用设计模式进一步提升性能。

最大限度地减少 CPU-GPU 内存传输并优化内存使用

GPU Coder 可对 MATLAB 代码段进行自动分析、识别和分区,以分别在 CPU 或 GPU 上运行。它还最大程度地减少了 CPU 与 GPU 之间的数据副本量。使用性能分析工具确定其他潜在瓶颈。

调用优化库

使用 GPU Coder 生成的代码会调用优化的 NVIDIA CUDA 库,包括 TensorRT、cuDNN、cuSolver、cuFFT、cuBLAS 和 Thrust。从 MATLAB 工具箱函数生成的代码也会尽可能映射到优化库。

使用设计模式进一步加速

设计模式(如模板处理)使用共享内存来提高内存带宽。使用某些函数(如卷积)时,将自动应用设计模式。您还可以使用特定编译控制指令手动调用它们。

硬件原型

将算法自动转换为 CUDA 代码,以快速访问硬件。

在 NVIDIA Jetson 和 DRIVE 平台上开发原型

使用 GPU Coder Support Package for NVIDIA GPUs,自动将生成的代码交叉编译和部署到 NVIDIA Jetson 和 DRIVE 平台上。

通过 MATLAB 和生成的代码访问外设和传感器

通过 MATLAB 与 NVIDIA 目标进行远程通信,从网络摄像头和其他支持的外设获取数据,以便进行早期原型开发。将您的算法与外设接口代码一起部署到板卡,以便独立执行。

从原型到生产

将 GPU Coder 与 Embedded Coder 结合使用,以交互方式在 MATLAB 代码与生成的 CUDA 代码之间进行追溯。通过软件在环 (SIL) 和处理器在环 (PIL) 测试,验证在硬件上运行的生成代码的数值行为。

加速算法

生成 CUDA 代码并进行编译以在 MATLAB 和 Simulink 内使用。

在 MATLAB 中使用 GPU 加速算法

在 MATLAB 代码中以 MEX 函数的形式调用生成的 CUDA 代码以加速执行,不过性能将因 MATLAB 代码本身的特性而异。对生成的 MEX 函数开展性能分析,以确定瓶颈并重点优化。

使用 NVIDIA GPU 加速 Simulink 仿真

您可以将 GPU Coder 与 Simulink Coder 结合使用,以在 NVIDIA GPU 上加速 Simulink 模型中 MATLAB Function 模块的计算密集型部分。